# **OPEN ACCESS**

# Electron Charge Transport in Non-Peripherally Substituted Copper Phthalocyanine

To cite this article: Nandu B. Chaure et al 2020 ECS J. Solid State Sci. Technol. 9 065003

View the article online for updates and enhancements.

# **Electron Charge Transport in Non-Peripherally Substituted Copper Phthalocyanine**

Nandu B. Chaure,<sup>1,2,z</sup> S. Barard,<sup>1</sup> Isabelle Chambrier,<sup>3</sup> Andrew N. Cammidge,<sup>3</sup> and Asim. K. Ray<sup>1,4</sup>

<sup>1</sup>Centre of Materials Research, Queen Mary University of London, London E1 4NS, United Kingdom

<sup>2</sup>Department of Physics, Savitribai Phule Pune University, (formerly University of Pune) Pune—411007, India

<sup>3</sup>School of Chemistry, University of East Anglia, Norwich NR4 7TJ, United Kingdom

<sup>4</sup>Brunel University London, Uxbridge, Middlesex UB8 3PH, United Kingdom

Bottom-gate, bottom-contact organic thin film transistors (OTFTs) were fabricated using solvent soluble copper-1,4,8,11,15,18,22,25-octakis(hexyl)phthalocyanine as the active semiconductor layer. The compound was deposited as 70 nm thick spin-coated films onto gold source-drain electrodes supported on octadecyltrichlorosilane treated 250 nm thick SiO<sub>2</sub> gate insulator. The analysis of experimental results showed the n-type field effect behaviour. Devices annealed at 100 °C under vacuum were found to exhibit the field-effect mobility of 0.0989 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, with an on/off current modulation ratio of ~10<sup>6</sup>, a reduced threshold voltage of 0.7 V and a sub-threshold swing of 2.12 V decade<sup>-1</sup>. The variations in surface morphology of the devices are found reflected considerably in the electrical measurements. The device contact resistance was found to be decreased as the gate bias increased and also with the annealing.

© 2020 The Author(s). Published on behalf of The Electrochemical Society by IOP Publishing Limited. This is an open access article distributed under the terms of the Creative Commons Attribution 4.0 License (CC BY, http://creativecommons.org/licenses/ by/4.0/), which permits unrestricted reuse of the work in any medium, provided the original work is properly cited. [DOI: 10.1149/ 2162-8777/aba189]

Manuscript submitted May 29, 2020; revised manuscript received June 24, 2020. Published July 9, 2020. This paper is part of the JSS Focus Issue on Porphyrins, Phthalocyanines, and Supramolecular Assemblies in Honor of Karl M. Kadish.

In recent years, organic field-effect transistors (OFETs) have been extensively used in designing complementary integrated circuits for flexible smart cards, low-cost radio frequency identification (RFID) tags, and organic active matrix displays and sensors.<sup>1</sup> Fullerene derivatives are found to be good materials for the formation of n-type conducting channels.<sup>2</sup> For example, a value of 0.34 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> for electron mobility is reported for the Faux-hawk fullerenes (C<sub>60</sub>FHF) channel.<sup>3</sup> Alternatively perylene diimides (PDIs) and naphthalene diimides (NDIs) are the most promising electron deficient building blocks for obtaining high performance electron transport materials with high mobilities of 6.2 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> due to their relatively high electron affinities, and excellent chemical and thermal stability.<sup>4</sup>

Solution processable organic and polymeric semiconducting materials are attractive to realize low-cost, high-volume, large-area electronic circuits on flexible substrates. Several solution based processes, such as spin-coating, drop-casting, and inkjet printing can be used to form semiconducting thin films. Bottom-gate, top-contact OTFTs with NDI active layers were fabricated based on OTSmodified SiO<sub>2</sub> substrates and extremely high electron mobility up to 7.5  $\text{cm}^2 \text{V}^{-1} \text{s}^{-1}$  was achieved.<sup>5</sup> Representative examples of PDI derivatives with thin film mobilities over  $1.0 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$  are compounds with  $C_8H_{17}$  and  $C_{13}H_{27}$  alkyl chains substituted at the N-positions, respectively. The mobility of solution-processed perchlorinateddiperylenebisimide(C12-4CldiPBI) is found to be larger than 1.0 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> with the largest value of 4.65 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1.6</sup> Bottom-gate, top-contact OTFTs were fabricated with a NDI on OTS-modified SiO2 substrates, and extremely high electron mobility up to 7.5  $\text{cm}^{-2} \text{V}^{-1} \text{s}^{-1}$  was achieved when the devices were tested after 30 min equilibration in an argon atmosphere at low humidity. Small molecules based on azulene derivatives, dicyanomethyleneterminated quinoidal oligothiophenes, and isoindigo derivatives (3E,7E)-3,7-bis(2-oxoindolin-3-ylidene)benzo[1,2-b:4,5-b']di-

furan-2,6(3 H,7 H)-dione have been investigated for their uses as n-type active layers in OFETs, producing mobility in the order of 0.1 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup><sup>8</sup> When[6,6]-phenyl C61 butyric acid methyl ester is doped with (4-(1,3dimethyl-2,3-dihydro-1H-benzoimidazol-2-yl) phenyl)dimethylamine, the electron mobility is found to increase from 1.68  $\times 10^{-2}$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> to 0.124 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> for undoped

and doped layers, respectively.<sup>8</sup> A high value of 3  $\text{cm}^2 \text{V}^{-1} \text{s}^{-1}$  has recently been reported for electron mobility for phenylalkyl-substituted-benzo[de]isoquinolino[1,8-gh] quinolinetetracarboxylic diimide.<sup>9</sup>

Phthalocyanines, highly conjugated 18  $\pi$ -electron planar aromatic systems with a central cavity of sufficient size capable of coordinating different metal ions, are thermally and chemically stable and show excellent semiconducting properties for their applications including the fabrication of OTFTs.<sup>10</sup> Thermally deposited fluorinated copper phthalocyanines (F8CuPc) show nchannel OTFT characteristics under vacuum with the electron mobility of  $7.9 \times 10^{-4}$  cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> in vacuum of  $10^2$  Pa.<sup>11</sup> A value of 0.54 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> is obtained for electron mobility of thermally deposited bis(pentafluorophenoxy) silicon phthalocyanine(F-10-SiPc) at 140 °C.<sup>12</sup> Electron mobilities of OTFTs with a n-type polycrystalline channel of tin phthalocyanines (SnPcs) with tributylsilane and trihexylsilane axial functional groups is found to be higher than their silicon counterparts due to increased molecular interactions.<sup>13</sup> The introduction of substituents onto the phthalocyanine nucleus can confer new and useful properties upon the ring system.14

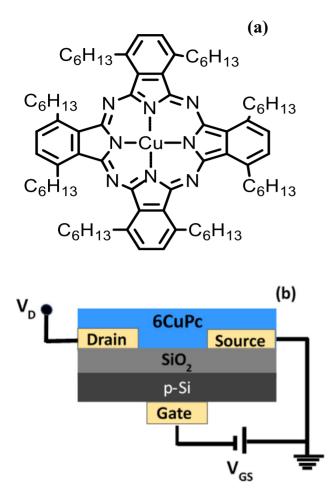

The present paper reports an investigation of n-type field-effect transistor characteristics of non-peripherally octakis(hexyl) substituted copper phthalocyanine (6CuPc) derivative in the bottom gate transistor configurations as shown in Fig. 1. As reported before, the solubility of these molecule in common organic solvents enabled it to be deposited readily as well-ordered films by the spin coating method, a methodology ideal for simple device fabrication at room temperature.<sup>15</sup> Hole transport in spin coated 6CuPc has been investigated in OTFTs of similar configurations, giving p-type characteristics in the accumulation mode. These molecules are liquid crystalline and the transistor parameters are reported to be dependent upon the annealing temperature. Devices heat treated at 100°C under vacuum ( $\ge 10^{-7}$ mbar) were found to exhibit the highest field-effect mobility of 0.7  $\text{cm}^2 \text{V}^{-1} \text{s}^{-1}$ , with an on-off current modulation ratio of 10<sup>7</sup>, threshold voltage of 2.0 V and a sub-threshold swing of 1.11 V per decade.<sup>16</sup>

#### Experimental

The drift mobility  $\mu_{de}$  was determined from the time of flight (TOF) measurement for the electron transport in a 9.1  $\mu$ m thick film

**Figure 1.** (a) Chemical structure of non-peripherally substituted 1,4,8,11,15,18,22,25-octakis(hexyl) copper phthalocyanine (6CuPc) and (b) bottom gate bottom contact organic field effect structure with channel length L and channel width W of 10  $\mu$ m and 2 mm respectively. The thickness of active6CuPc film layer is ~70 nm.

of 6CuPc sandwiched between two transparent indium tin oxide (ITO) coated glass substrates. The cell was formed by slow cooling of the organic layer at a rate of 2 °C min<sup>-1</sup> to room temperature from the isotropic melt and a film of anti-parallel polyimide was used as the alignment layer. The photocurrents were produced using a 532 nm pulsed output of a double-frequency Nd:YAG laser to excite the sample. The bias between the ITO electrodes was provided by a DC power supply while the transient photocurrent was recorded by a voltage drop across the input resistor of a gain 11 amplifier circuit whose output was connected to an Agilent Infinium digitizing oscilloscope. Signal averaging was carried out on all signals in order to improve data quality.<sup>17</sup>

As shown in Fig. 1b, measurements of the n-type transistor characteristics have been performed under identical conditions on bottom gated organic field effect transistors using both as-prepared and annealed 70 nm ( $\pm$  2 nm) thick spin-coated active layer 6CuPc films on the pre-patterned source and drain electrodes and 250 nm thick octaoctadecyltrichlorosilane (OTS) passivated SiO<sub>2</sub> gate dielectric layer on the highly doped silicon (110) gate electrode substrates. Two stage spin coater, Chemat Technology Inc., Model KW-4A was employed to prepare the uniform 6CuPc thin films initially at 1000 rpm for 30 s and subsequently 3000 rpm for 60 s. The devices were heated to 100 °C in a tubular furnace under vacuum of  $\sim 2 \times 10^{-7}$  Torr and then gradually cooled down to room temperature at the rate of 1 °C min<sup>-1</sup>. The electrical measurements were performed at room temperature in air under ambient conditions using a Keithley 4200 semiconductor parameter analyzer with three

source measure units (SMUs), which allows to measure the source, drain and gate currents simultaneously. All measurements were performed at a typical scan rate 50 m V s<sup>-1</sup>. A custom-made probe station was used to obtain the source, drain and gate contacts. Prior to electrical measurement the devices were blew with N<sub>2</sub> gas and all equipments commonly grounded to probe station.<sup>18</sup> The surface morphology of the sample was investigated by the Digital Nanoscope III, Atomic Force Microscope (AFM) in non-conducting mode at ambient conditions using V-shaped silicon nitride cantilevers with force constant 2 N/m and resonance frequency 315 kHz.

## **Results and Discussion**

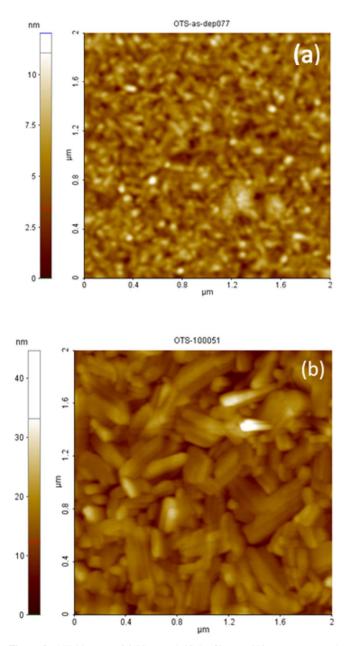

The AFM micrographs o as-prepared and annealed 6CuPc spin coated film on Silicon substrate is shown in Figs. 2a and 2b, respectively. Both films illustrate significantly void free, densely packed compact good film adhesion to the 15 mm  $\times$  15 mm area of silicon substrate. Long grain like flat lying crystals of size  $\sim 0.1 \ \mu m$ can be seen in as-prepared sample. Randomly oriented short nanorods  $\sim 0.3$  to 0.4  $\mu$ m were observed upon annealing the devices at 100 °C in vacuum. The rod like morphology reduces apparent grain boundaries and may behave like a compound in the bulk material. Further, the rod like morphology is assumed to be supportive for charge transportation within the active semiconductor. which of course helps to improve the mobility of device. Root mean square values of 9 nm and 17 nm were measured for surface roughness of as-prepared and annealed 6CuPc films, respectively. The number of grain boundaries influences the electrical properties of devices. Rosenwaks and co-worker showed for the accumulation of charge carriers at the grain boundaries for pentacene films using Kelvin probe measurements leads to lower mobility of FETs. Klauk and co-worker have reported that the grain boundaries are major source of degradation of charge carries mobility in C<sub>3</sub>F<sub>7</sub>CH<sub>2</sub>-PTCDI-(CN)<sub>2</sub> based p-channel devices.<sup>20</sup> Larger grain size obtained for pentacene on poly-4-vinylphenol than polymethyl methacrylate gate dielectric measured higher mobility.

The transit times  $t_0$  of the photo-generated carriers traversing the 6CuPc layer at an applied bias, were determined by the inflection point on a double logarithmic plot. The resulting mobilities  $\mu$  were then calculated using the relation,

$$\mu_{\rm de} = \frac{d^2}{Vt_0} \tag{1}$$

where d is the cell thickness and V is the applied bias. Electron transport was measured in the sample at 0.40  $\mu$ s and 0.26  $\mu$ s for -6 V and -10V, respectively (Fig. 3a). Further analysis of the sample at higher fields for both electron transport, could not be carried out at room temperature as the inflexion point became engulfed in the initial peak of the photocurrent. The mobilities were calculated using Eq. 1 and plotted against the square root of the electric field (Fig. 3b). Electron mobility is found to be 0.4 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. This value is three orders of magnitude higher than one obtained for similar configured 2  $\mu$ m thick 6ZnPc drop-cast films.<sup>22</sup> This relatively high mobility is attributed to the larger, well defined 6CuPc crystallites formed during slow cooling of the sample. For both bias voltages, the photo-current is found to have progressively decreased over time. However, the decrease is steeper for  $V_a = 10 V$ than  $V_a = 23$  V, indicating the dominance of dispersive transport. The time of flight method gives a "long-range" mobility measured over relatively large distances (usually tens of microns) and on a milli-second or micro-second timescale. This dispersive behaviour is consistent for the multi-domain film structure, consisting of a large number of boundaries between domains with typically 300 nm to 400 nm cross-section as recorded under a polarizing microscope.

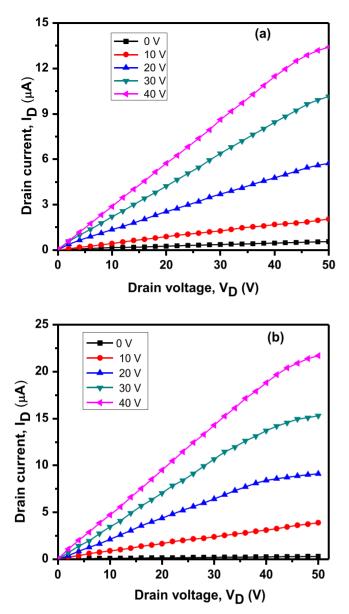

A typical set of output characteristics of drain-to-source current  $I_{DS}$  vs drain-to-source voltage  $V_{DS}$  for different values of the gate voltage  $V_G$  of as-prepared and annealed devices are shown in Figs. 4a and 4b, respectively. The variations in surface morphology

Figure 2. AFM images of OTS treated 6CuPc films on SiO $_2$  (a) as-prepared and (b) annealed at 100  $^\circ\text{C}.$

of the devices are found reflected considerably in the electrical measurements. Both devices demonstrated a typical n-type behaviour operating in accumulation mode with the increase in the drain current  $I_{DS}$  with  $V_{G}$ .<sup>23</sup> A significant improvement in the performance of thermally annealed device at 100 °C is observed due to the coalescence of small grains having low surface energy leading to improve crystallinity and less grain boundaries. A clear transition from linear to saturation region was observed for annealed device due to pinch-off of the accumulation of charges. It was further observed that the  $I_{DS}$  in annealed device saturated at lower  $I_{DS}$  as compared to the corresponding value of as-prepared device. The annealing temperature was chosen based on the differential scanning calorimetry studies discussed in our earlier publication.<sup>16</sup>

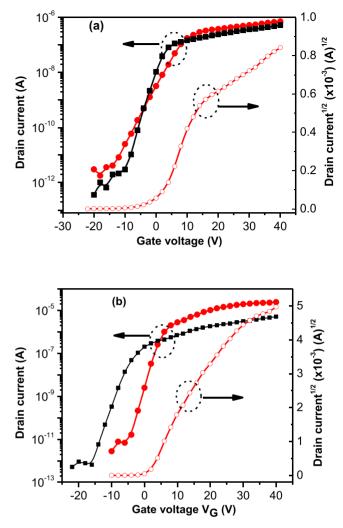

The transfer characteristics, drain-to-source current,  $I_{DS}$  and square root of drain current,  $(I_{DS})^{1/2}$  as a function of gate voltages,  $(V_G)$  with constant drain voltages in linear regime,  $V_D = 5$  V and saturated regime,  $V_D = 40$  V for as-prepared and annealed devices are shown in Figs. 5a and 5b, respectively. The performance

**Figure 3.** (a) Electron photocurrent transients in a 9.1  $\mu$ m thick cell of 6CuPc at -6 V and -10 V, scaling linearly with field, (b) electron mobility in 6CuPc calculated, parametric in electric field.

parameters of 6CuPc FET were extracted from the saturated and linear regimes by using the Eqs. 2 and 3.

$$I_{DS(sat)} = \frac{WC_i}{2L} \mu_{sat} (V_G - V_T)^2$$

[2]

$$\mu_{\rm lin} = \left(\frac{\rm L}{\rm WC_i V_{\rm DS}}\right) \frac{\partial \rm I_{\rm DS}}{\partial \rm V_{\rm G}}$$

[3]

where L, W and C<sub>i</sub> are the channel length (10  $\mu$ m), channel width (2 mm) and capacitance/unit area taken to be  $1 \times 10^{-4}$  F m<sup>-2</sup> for the OTS treated SiO<sub>2</sub> gate dielectrics.<sup>24</sup>  $\mu_{sat}$  and  $\mu_{lin}$  are saturated and linear field effect mobility, V<sub>T</sub> is the threshold voltage of the device in both linear and saturated regime were determined from the graph of  $\sqrt{I_{DS}}$  vs V<sub>G</sub> by extrapolating the straight line to  $I_{DS} = 0$ . The values of linear and saturated field effect mobility,  $\mu_{lin}$  and  $\mu_{sat}$  were extracted from the trans-conductance plot shown in Figs. 5a and 5b. The values of mobilities of as-prepared and annealed devices are given in Table I. The value of  $\mu_{lin}$  was comparatively lower than that of  $\mu_{sat}$ . However, the value of  $\mu_{lin}$  is found to be increased by one order of magnitude from  $3.69 \times 10^{-3}$  cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> for OFFT with as-prepared channel to  $4.87 \times 10^{-2}$  cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup> for annealed OFETs. Values of  $\mu_{sat}$  at V<sub>G</sub> = 40 V are found to be  $3.67 \times 10^{-2}$  cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup> for as-prepared and annealed 6CuPc OTFTs, respectively. The value of  $\mu_{sat}$  measured for annealed device is more than doubled as compared to the as-

Figure 4. Output characteristics for an OTFT with the 6CuPc films in terms of the variation of the drain current I<sub>D</sub> as a function of the drain voltage  $V_D$ , (a) as-deposited and (b) annealed for the gate voltage  $V_G = 0$  V, 10 V, 20 V, 30 V and 40 V.

prepared device. These experimental results show the decrease of the resistance of the conducting channel with large grain boundaries leading to a performance improvement of the OTFTs.<sup>25</sup> The transistor characteristics of an n-type OTFT using physical vapour deposited N hexdecafluoro copper phthalocyanine (16-CuPc) films as active layer have recently reported. Values of saturation mobility  $\mu_{sat}$  threshold voltage  $V_T$  and on-off ratio are found to be  $2 \times 10^{-2}$  cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup>, -16 V and  $3 \times 10^3$ , respectively. In this context, 6CuPc OTFTs have produced the characteristics of improved performance.<sup>26</sup> Kraus et al., and de Boer et al., showed the ambiploar behaviour of CuPc OFETs prepared by thermal evaporation technique with electron mobility to  $5.8 \times 10^{-3}$  and  $10^{-5}$ - $10^{-3}$  cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup>, <sup>27,28</sup> which is considerably less than the electron mobility,  $9.89 \times 10^{-2}$  cm<sup>2</sup> V<sup>-1</sup>s<sup>-1</sup> and production the electron mobility.

The transfer characteristics exhibited good sub-threshold slopes. The sub-threshold voltage, S gives the information about the gate voltage required to increase the drain-to-source current by a factor of 10. The values of sub-threshold voltages, 3.65 V decade<sup>-1</sup> and 2.12 V decade<sup>-1</sup> were estimated using the following equation for as-

Figure 5. Transfer characteristics for 6CuPc (a)  $V_{\rm D}=5$  V and (b)  $V_{\rm D}=40$  V for as-deposited and annealed devices.

prepared and annealed 6CuPc transistors within saturated regimes, respectively.

$$S = \frac{dV_G}{d(\log_{10} I_{DS})}$$

[4]

The performance parameters of the transistor also depend on the grain size, grain boundaries and the interface between the gate dielectric (SiO<sub>2</sub>) layer and active semiconductor (6CuPc) thin film. The density of trapped charges (trap charge density ( $N_t$ ) can be determined by using the following relation related to sub-threshold voltages:

$$N_{t} = \left[\frac{S \log (e)}{\left(\frac{kT}{q}\right)} - 1\right] \frac{C_{i}}{q}$$

[5]

where k, T, q and S are the Boltzmann constant, the operating temperature, the electronic charge and the sub-threshold voltage swing, respectively. The values of density of trap,  $N_t$  were calculated to be  $1.99 \times 10^{12}$  cm<sup>-2</sup> eV<sup>-1</sup> and  $2.23 \times 10^{11}$  cm<sup>-2</sup> eV<sup>-1</sup> for asprepared and annealed devices in the saturated regime. The decrease in value of  $N_t$  upon annealing is believed to be due to reduction in grain boundaries.<sup>29</sup>

| Table I. A summary of transistor parameters measured for as-prepared and annealed 6CuPc dev | ices. |

|---------------------------------------------------------------------------------------------|-------|

|---------------------------------------------------------------------------------------------|-------|

|                         | Mobility (cm <sup>2</sup> Vs <sup>-1</sup> ) |                   |                      |                              |                                      |                                                                           |                                                                           |  |

|-------------------------|----------------------------------------------|-------------------|----------------------|------------------------------|--------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------|--|

| 6CuPctransistors        | $\mu_{\mathrm{sat}}$                         | $\mu_{ m lin}$    | On/off<br>ratio      | Threshold voltage, $V_T$ (V) | Sub-threshold voltage, S (V/ decade) | Interface trap density, $N_t (cm^{-2} eV^{-1})$                           | Grain-boundary trap density $(cm^{-3})$                                   |  |

| As-prepared<br>Annealed | 0.0367<br>0.0989                             | 0.00369<br>0.0487 | $10^{5}$<br>$10^{6}$ | 1.0<br>0.7                   | 3.65<br>2.12                         | $\begin{array}{c} 1.99 \times 10^{12} \\ 2.23 \times 10^{11} \end{array}$ | $\begin{array}{c} 6.56 \times 10^{12} \\ 1.72 \times 10^{12} \end{array}$ |  |

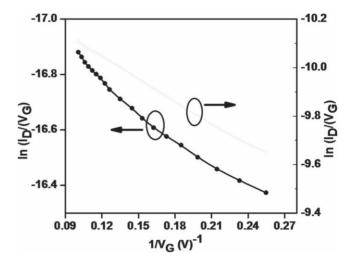

The relation between  $I_{DS}$  and the charges trapped at the grain boundaries of the material is described by Levinson model.<sup>30</sup> The Levinson plots of  $ln(I_D/V_G)$  vs  $1/V_G$  at  $V_D = 40$  V for as-prepared and annealed 6CuPc devices are shown in Fig. 6. The linear behaviour of the graph demonstrates the dependence of  $I_{DS}$  on the density of traps at the grain boundaries,  $N_g$ .

$$I_{DS} = \mu_0 V_{DS} \frac{W}{L} C_i V_G \exp\left(-\frac{q^3 N_g^2 t}{8\varepsilon_0 \varepsilon_{Pc} k T C_i V_G}\right)$$

[6]

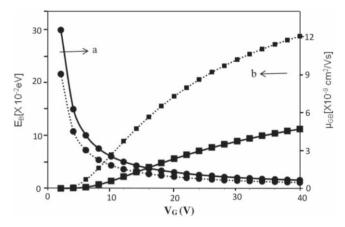

The values of N<sub>g</sub> and trap-free mobility,  $\mu_0$  can be extracted from the slope and intercept to x-axis at  $1/V_G = 0$ , respectively. The values of free space permittivity,  $\varepsilon_o = 8.85 \times 10^{-12} \, \mathrm{F \, m^{-1}}$ , electronic charge,  $q = 1.6 \times 10^{-19} \, \mathrm{C}$ , Boltzmann constant,  $k = 8.62 \times 10^{-5} \, \mathrm{eV \, K^{-1}}$ , temperature,  $T = 300 \, \mathrm{K}$  and dielectric constant,  $\varepsilon_{pc} = 3$  of 6CuPc were used to determine values of N<sub>g</sub>. The values of  $6.56 \times 10^{12} \, \mathrm{cm^{-3}}$  and  $8.72 \times 10^{11} \, \mathrm{cm^{-3}}$  were estimated for N<sub>g</sub>, from the slopes of best linear fits of Levinson plots. As shown in Fig. 7, the value of N<sub>g</sub> obtained for annealed device is smaller than that of as-deposited film by nearly a one order of magnitude. This observation is associated with the less dense presence of grain boundaries upon thermal annealing. The values of trap-free mobilities,  $0.882 \times 10^{-2} \, \mathrm{and} \, 2.26 \times 10^{-2} \, \mathrm{cm^2 \, V^{-1} \, s^{-1}}$  at  $V_D = 40 \, \mathrm{V}$  were calculated for as-prepared and annealed 6CuPc devices. The grain boundary barrier  $E_B = \frac{2000 \, \mathrm{ere}}{8 \varepsilon_{0.5}^{0.5} \mathrm{ere} \mathrm{V}_0}$  decreases while the grain boundary mobility  $\mu_{GB}$  increases with V<sub>G</sub>. E<sub>B</sub> is found to undergo sharp decreases at low voltages and then the reduction tends to be steady. The density N<sub>g</sub> is believed to contribute to the parasitic resistance of the device.

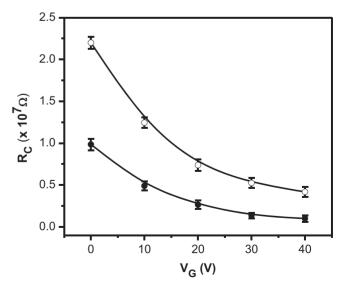

The contact resistance  $R_C$  can be expressed at each gate voltage in the following form<sup>31</sup>:

$$R_{\text{total}}\left(\frac{W}{L}\right) = \frac{1}{\mu_{\text{lin}}C_{\text{i}}(V_{\text{G}} - V_{\text{T}})} + R_{\text{C}}\left(\frac{W}{L}\right)$$

[7]

The linear regions of the output curve can be used to determine the values of total resistance ( $R_{total}$ ) for different gate voltages. The linear mobilities, 0.00369 and 0.0487 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> computed with  $V_D = 5 V$  for as-prepared and annealed transistors, respectively along with corresponding  $V_G$  and  $V_T$  were used. The contact resistances as a function of gate biases shown in Fig. 8 revealed that the contact resistance decreases with increasing the gate bias. The decrease in contact resistance at higher gate biases could be due to the higher charge density in the conducting channel and in the vicinity of contacts. These results are consistent with the observations reported by Zhang et al.<sup>32</sup> Upon annealing the contact resistances obtained for each gate bias decreases substantially due to the coalescence of small grains, results the improvement in degree of crystallinity and less grain boundaries.

# **Concluding Remarks**

6CuPc molecules are liquid crystalline and remain well aligned in the spin coated film with their columnar axis parallel to the substrate. This technique of thin film deposition may easily be adopted for the deposition over a large area for flexible electronics. The disordered film structure is evident from AFM images, following the annealing temperature dependent growth of crystallites in different shapes, sizes and orientations. The variations in surface morphology of the devices are found reflected considerably in the electrical measurements. The drain-source current is believed to be one dimensional electron transport via the overlap of  $\pi$ - $\pi$  molecular orbitals through the accumulation layer. This investigation is interesting for the development of organic complementary metal oxide semiconductor (CMOS) circuits and organic light-emitting transistors.

Figure 6. Levinson plots for as-prepared (open circles) and annealed (closed circles) of 6CuPc devices for  $V_D = 40$  V.

**Figure 7.** Dependence of (a) interfacial barrier  $E_B$  (curves with closed circles) and (b) the grain boundary mobility  $\mu_{GB}$  (curve with solid rectangles) on gate voltage  $V_G$  for deposited (solid lines) and (broken lines) annealed 6CuPc films.

Figure 8. Dependence of the contact resistance  $R_C$  on the gate voltage  $V_G$  for as-deposited (open circles) and annealed (closed circles) 6CuPc films.

## Acknowledgments

Experimental work was carried out at Queen Mary, University of London under financial support from the UK Technology Strategy Board (Project No. TP/6/EPH/6/S/K2536J). The pre-patterned substrates were prepared by QUDOS Technology, Rutherford Appleton Laboratory, Didcot, UK.

# ORCID

## Nandu B. Chaure (1) https://orcid.org/0000-0002-4134-5019

#### References

- 1. B. Kumar, B. K. Kaushik, and Y. S. Negi, "Thin film transistors: structures, models, materials, fabrication, and applications: a review." Polym. Rev., 54, 33 (2014).

- 2. P. H. Wobkenberg, D. D. C. Bradley, D. Kronholm, J. C. Hummelen, D. M. de Leeuw, M. Colle, and T. D. Anthopoulos, "High mobility n-channel organic fieldeffect transistors based on soluble C-60 and C-70 fullerene derivatives." Synth. Met., 158, 468 (2008).

- 3. S. Y. Liu, N. J. DeWeerd, B. J. Reeves, L. K. San, D. Dahal, R. K. R. Krishnan, S. H. Strauss, O. V. Boltalina, and B. Lussem, "Doped N-type organic field-effect transistors based on faux-hawk fullerene." Adv. Electron. Mater., 5, 1900109 (2019).

- 4. A. Nowak-Krol, K. Shoyama, M. Stolte, and F. Wurthner, "Naphthalene and pervlenediimides-better alternatives to fullerenes for organic electronics?" Chem. Commun., 54, 13763 (2018)

- 5. S. Kola, J. Sinha, and H. E. Katz, J. Polym. Sci. Pt. B-Polym. Phys., 50, 1090 (2012).

- 6. A. F. Lv et al., "High mobility, air stable, organic single crystal transistors of an ntype diperylenebisimide." Adv. Mater., 24, 2626 (2012).

- 7. K. Zhou, H. L. Dong, H. L. Zhang, and W. P. Hu, "High performance n-type and ambipolarsmallorganicsemiconductors for organicthin film transistors." Phys. Chem. Chem. Phys, 16, 22448 (2014).

- 8. J. T. E. Quinn, J. X. Zhu, X. Li, J. L. Wang, and Y. N. Li, J. Mater. Chem. C, 5, 8654 (2017).

- 9. T. Okamoto et al., Sci. Adv., 6, eaaz0632 (2020)

- 10. C. G. Claessens, U. Hahn, and T. Torres, "Phthalocyanines: from outstanding electronic properties to emerging applications." Chem. Rec., 8, 75 (2008).

- 11. A. Matumoto, N. Hoshino, T. Akutagawa, and M. Matsuda, "N-Type semiconducting behavior of copper octafluorophthalocyanine in an organic field-effect transistor." Appl. Sci.-Basel, 7, 1111 (2017).

- 12. O. A. Melville, T. M. Grant, B. Mirka, N. T. Boileau, J. Park, and B. Lessard, "Ambipolarity and air stability of silicon phthalocyanine organic thin-film transistors." *Adv. Electron. Mater.*, **5**, 1900087 (2019).

- 13. T. M. Grant, N. A. Rice, L. Muccioli, F. Castet, and B. Lessard, "Solutionprocessable n-type tin phthalocyanines in organic thin film transistors and as ternary additives in organic photovoltaics." ACS Appl. Electron. Mater., 1, 494 (2019).

- T. A. Turkmen et al., *Inorg. Chem.*, **57**, 6456 (2018).

S. Y. Wang, X. L. Zhao, Y. H. Tong, Q. X. Tang, and Y. C. Liu, *Adv. Mater.* Interfaces, 7, 1901950 (2020).

- 16. N. B. Chaure, C. Pal, S. Barard, T. Kreouzis, A. K. Ray, A. N. Cammidge, I. Chambrier, M. J. Cook, C. E. Murphy, and M. G. Cain, J. Mater. Chem., 22, 19179 (2012).

- 17. S. Barard, T. Kreouzis, A. N. Cammidge, M. J. Cook, and A. K. Ray, Semicond. Sci. Technol., 33, 095010 (2018).

- 18. N. B. Chaure, J. L. Sosa-Sanchez, A. N. Cammidge, M. J. Cook, and A. K. Ray, Org. Electron., 11, 434 (2010).

- 19. S. Yogev, R. Matsubara, M. Nakamura, and Y. Rosenwaks, Org. Electron., 11, 1729 (2010).

- 20. R. T. Weitz, K. Amsharov, U. Zschieschang, M. Burghard, M. Jansen, M. Kelsch, B. Rhamati, P. A. van Aken, K. Kern, and H. Klauk, Chem. Mater., 21, 4949 (2009)

- 21. G.-W. Kang, K.-M. Park, J.-H. Song, C. H. Lee, and D. H. Hwang, Curr. Appl Phys., 5, 297 (2005).

- 22. N. B. Chaure, S. Barard, A. K. Ray, A. N. Cammidge, and M. J. Cook, EPL, 104, 57005 (2013).

- 23. I. A. Grimaldi, M. Barra, A. Carella, F. V. Di Girolamo, F. Loffredo, C. Minarini, F. Villani, and A. Cassinese, Synth. Met., 176, 121 (2013).

- 24. N. B. Chaure, A. N. Cammidge, I. Chambrier, M. J. Cook, and A. K. Ray, ECS J. Solid State Sci. Technol., 4, P3086 (2015).

- 25. J. Xu, X. Q. Liu, L. WangH., W. L. Hou, L. L. Zhao, and H. Q. Zhang, Solid-State Electron., 127, 61 (2017).

- 26. N. T. Boileau, O. A. Melville, B. Mirka, R. Cranston, and B. H. Lessard, RSC Adv., 9, 2133 (2019).

- 27. M. Kraus, S. Richler, A. Opitz, W. Brütting, S. Haas, T. Hasegawa, A. Hinderhofer, and F. Schreiber, J. Appl. Phys., 107, 094503 (2010).

- 28. R. W. I. de Boer, A. F. Stassen, M. F. Craciun, C. L. Mulder, A. Molinari, S. Rogge, and A. F. Morpurgoa, Appl. Phys. Lett., 86, 262109 (2005).

- G. H. Heilmeier and S. E. Harrison, *Phys. Rev.*, **132**, 2010 (1963).

J. Levinson, F. R. Shepherd, P. J. Scanlon, W. D. Westwood, G. Este, and M. J. Rider, Appl. Phys., 53, 1193 (1982).

- 31. M. Waldrip, O. D. Jurchescu, D. J. Gundlach, and E. G. Bittle, Adv. Funct. Mater., 30, 1904576 (2020).

- 32. K. Zhang, N. B. Kotadiya, X. Y. Wang, G. J. A. H. Wetzelaer, T. Marszalek, PisulaW., and P. W. M. Blom, Adv. Electron. Mater., 6, 1901352 (2020).